Intel, AMD a další těžké váhy v oboru vytvářejí nový standard chipletů

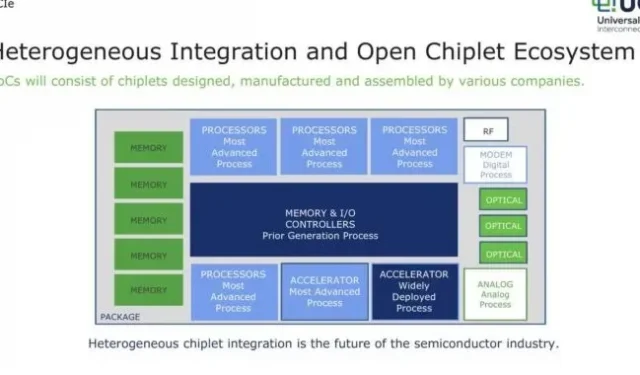

Někteří z největších výrobců procesorů, včetně Intel, AMD, Qualcomm, Arm, TSMC a Samsung, se spojili, aby definovali nový standard pro procesory založené na čipech. Nový standard nazvaný Universal Chiplet Interconnect Express (zkráceně UCIe) si klade za cíl definovat otevřený, interoperabilní standard pro kombinování více křemíkových matric (či čipů) do jednoho balíčku.

Intel, AMD a další již vyvíjejí nebo prodávají procesory založené na čipech v té či oné podobě – většina procesorů AMD Ryzen čiplety používá a budoucí procesory Intel Sapphire Rapids Xeon budou také. Všechny tyto čipy však používají různá propojení, která umožňují komunikaci mezi čipy. Standard UCIe, pokud uspěje, nahradí je jednotným standardem, čímž teoreticky malým firmám usnadní používání čipových sad nebo použití čipů jiné společnosti ve vlastních produktech.

Návrhy založené na čipech jsou výhodné pro výrobu velkých čipů v pokročilých výrobních závodech, částečně proto, že snižují množství křemíku, kterým musí výrobci plýtvat. Pokud výrobní vada postihne jedno jádro CPU, vyhodit (nebo odstranit) jeden 8jádrový čiplet je mnohem levnější než vyhodit obrovskou kostku 16 nebo 32jádrového CPU. Design čipů také umožňuje kombinaci čipů a výrobních procesů. Můžete například použít starší, levnější proces pro čipovou sadu a novější, pokročilejší proces pro jádra procesoru a mezipaměti. Nebo můžete dát AMD GPU do stejného pouzdra jako procesor Intel.

Podle AnandTech bude standard UCIe pokrývat fyzickou a protokolovou vrstvu návrhu čipu. Standard bude definovat, jak by měly být čipy vzájemně propojeny, a protokol pro usnadnění komunikace mezi čipy. Návrháři čipů však budou moci tyto čipy zabalit, jak uznají za vhodné, což umožní čipům komunikovat mezi sebou přímo přes substrát pouzdra nebo pomocí nějakého druhu můstku na bázi křemíku nebo jiného prostředníka.

Pro zohlednění těchto různých možností fyzického balení definuje UCIe verze 1.0 dvě různé úrovně výkonu. Balíček „Standard“ vyžaduje 16 datových pruhů a až 25 mm prostoru mezi čipovými sadami, zatímco balíček „Extended“ využívá 64 datových pruhů a povoluje pouze 2 mm prostoru.

Protokoly, které jsou základem UCIe, jsou PCI Express a související standardy Compute Express Link (CXL), které jsou výrobcům čipů dobře známé. Ale společnosti, které již vyvinuly pokročilejší nebo specializované protokoly pro komunikaci mezi čipovými sadami, jako je AMD a její Infinity Fabric , budou moci tyto protokoly používat, a přitom zůstanou kompatibilní s UCIe. UCIe byl původně vyvinut společností Intel a poté darován širší skupině UCIe, aby sloužil jako základ pro nový standard. Ale členské společnosti skupiny „začnou spolupracovat na technologii UCIe nové generace“ koncem tohoto roku.

Pokud potřebujete více technických podrobností o standardu UCIe, bílou knihu najdete zde .

Výpis obrázků od AMD

Napsat komentář