Intel, AMD og andre sværvægtere i industrien er ved at skabe en ny chiplet-standard

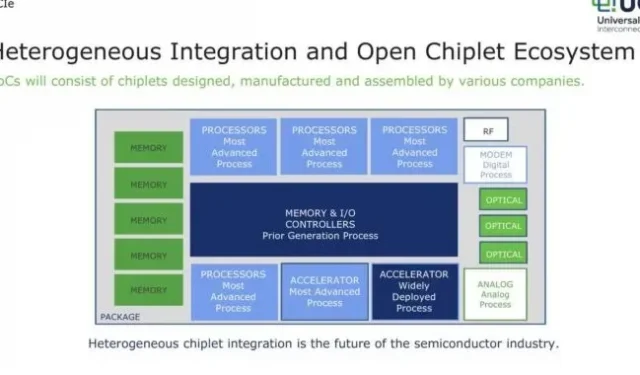

Nogle af de største processorproducenter, herunder Intel, AMD, Qualcomm, Arm, TSMC og Samsung, går sammen om at definere en ny standard for chip-baserede processorer. Den nye standard, kaldet Universal Chiplet Interconnect Express (forkortet UCIe), har til formål at definere en åben, interoperabel standard til at kombinere flere silicium-matricer (eller chiplets) i en enkelt pakke.

Intel, AMD og andre udvikler eller sælger allerede chiplet-baserede processorer i en eller anden form – de fleste AMD Ryzen-processorer bruger chiplets, og fremtidige Intel Sapphire Rapids Xeon-processorer vil også. Men alle disse chips bruger forskellige sammenkoblinger for at muliggøre kommunikation mellem chiplets. UCIe-standarden, hvis den lykkes, vil erstatte dem med en enkelt standard, hvilket teoretisk gør det lettere for små virksomheder at bruge chipsæt eller bruge en anden virksomheds chips i deres egne produkter.

Chip-baserede designs er gavnlige til fremstilling af store spåner på avancerede produktionssteder, til dels fordi de reducerer mængden af silicium, som producenterne skal spilde. Hvis en produktionsfejl påvirker en CPU-kerne, er det meget billigere at smide (eller fjerne) en 8-core chiplet end at smide en enorm 16- eller 32-core CPU-matrice væk. Chipdesign tillader også kombinationen af chips og fremstillingsprocesser. For eksempel kan du bruge en ældre, billigere proces til dit chipset og en nyere, mere avanceret proces til processorkerner og caches. Eller du kan sætte en AMD GPU i samme etui som en Intel-processor.

Ifølge AnandTech vil UCIe-standarden dække de fysiske lag og protokollag af chipdesign. Standarden vil definere, hvordan chiplets skal forbindes til hinanden og en protokol for at lette kommunikationen mellem chiplets. Men chipdesignere vil frit kunne pakke disse chiplets, som de finder passende, hvilket gør det muligt for chiplets at kommunikere med hinanden direkte gennem pakkesubstratet eller ved at bruge en form for siliciumbaseret bro eller anden mellemled.

For at tage højde for disse forskellige fysiske pakkemuligheder, definerer UCIe version 1.0 to forskellige niveauer af ydeevne. “Standard”-pakken kræver 16 databaner og op til 25 mm plads mellem chipsæt, mens den “Udvidede”-pakke bruger 64 databaner og kun tillader 2 mm plads.

Protokollerne bag UCIe er PCI Express og de relaterede Compute Express Link (CXL) standarder, som er velkendte af chipproducenter. Men virksomheder, der allerede har udviklet mere avancerede eller dedikerede protokoller til kommunikation mellem chipsæt, såsom AMD og dets Infinity Fabric , vil være i stand til at bruge disse protokoller, mens de forbliver UCIe-kompatible. UCIe blev oprindeligt udviklet af Intel og derefter doneret til den bredere UCIe-gruppe for at tjene som grundlag for en ny standard. Men gruppens medlemsvirksomheder “begynder at arbejde sammen om næste generation af UCIe-teknologi” fra senere i år.

Har du brug for flere tekniske detaljer om UCIe-standarden, kan du finde hvidbogen her .

Billedliste fra AMD

Skriv et svar