Intels største bærbare CPU-opdatering i årevis er en stor afvigelse fra tidligere designs

Intels næste generation Meteor Lake bærbare processorer er ved at blive frigivet – virksomheden annoncerede i denne uge, at de første processorer vil lanceres den 14. december. Det er uklart, om de faktiske Core- og Core Ultra-systemer vil være tilgængelige til køb på den dato, men som et absolut minimum , vil den officielle meddelelse bane vejen for mange bærbare meddelelser på CES i januar.

Vi kender allerede en masse grundlæggende fakta om Meteor Lake; den bruger en kombination af chiplets fremstillet af både Intel og TSMC i stedet for en enkelt monolitisk die, og det vil markere pensioneringen af Intels “n. generation” og i3/i5/i7/i9 branding. Vi ved også, at den ikke vil være klar til desktops, og at den næste runde af Core desktop-CPU’er vil være meget lig 12. og 13. generations chips.

Men ved Intels Innovation-begivenhed i denne uge dykkede virksomheden lidt dybere ned i nogle af Meteor Lakes fremskridt, og beskrev mere om, hvordan chipsene ville balancere E-kerner og P-kerner og annoncerede sin mest omfattende integrerede GPU-opgradering i årevis. Vi rammer nogle højdepunkter nedenfor, selvom det er værd at se eller læse hele præsentationen for at finde ud af mere.

Fliser for miles

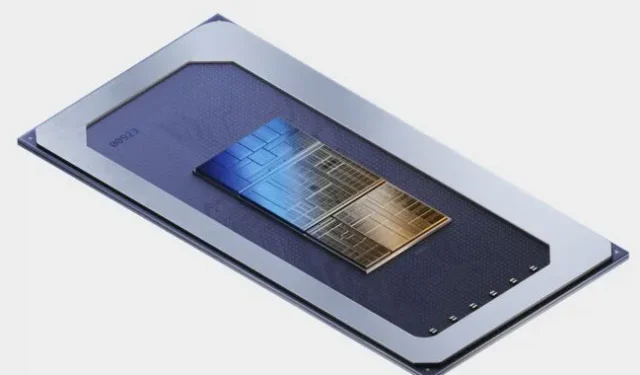

Meteor Lake vil være Intels første forbrugerprocessor, der flytter til et chiplet-baseret design – i stedet for at være én monolitisk die, der indeholder CPU’en, GPU’en og alle de andre bits og stykker, der er nødvendige for en moderne bærbar CPU, er Meteor Lake opdelt i fire “fliser”, der er sat sammen af en femte basisflise, der giver dem mulighed for at kommunikere med hinanden. Processen med at stable chiplets oven på basisflisen er en pakketeknologi, som Intel kalder Foveros .

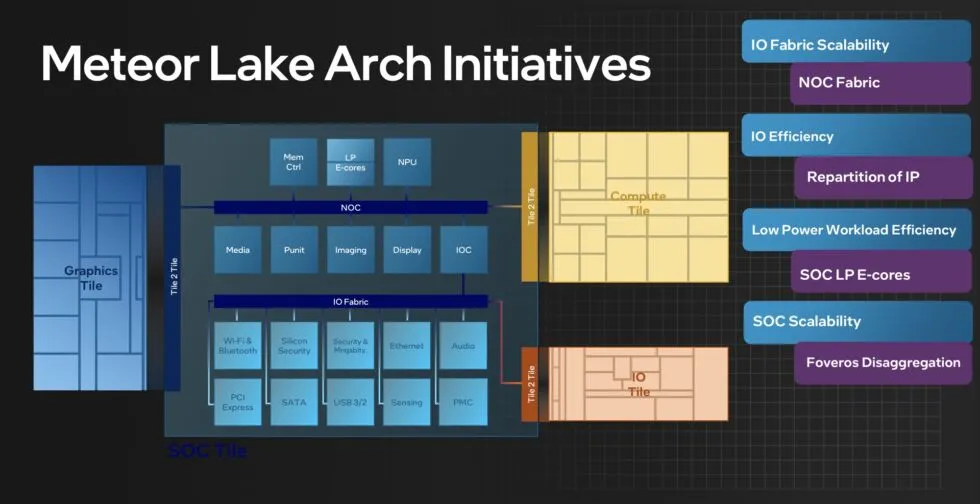

Her er en grundlæggende opdeling af, hvad der er i hver af disse fire fliser:

- Computerflisen er der , hvor det meste af den faktiske CPU er. Intels nuværende gengivelser viser en chip med seks højtydende P-kerner baseret på Redwood Cove-arkitekturen og otte højeffektive E-kerner baseret på Crestmont-arkitekturen.

- Grafikflisen er der, hvor det meste af grafikbehandlingen foregår, selvom nogle få specifikke funktioner, som du normalt finder i en GPU, er blevet flyttet til andre fliser . Meteor Lakes integrerede GPU er for det meste kun en integreret version af en Intel Arc dedikeret GPU, komplet med hardware-ray-tracing-acceleration.

- IO -flisen håndterer de fleste eksterne tilslutningsmuligheder, inklusive PCI Express 5.0-baner og Thunderbolt 4-understøttelse ( Thunderbolt 5 skal vente).

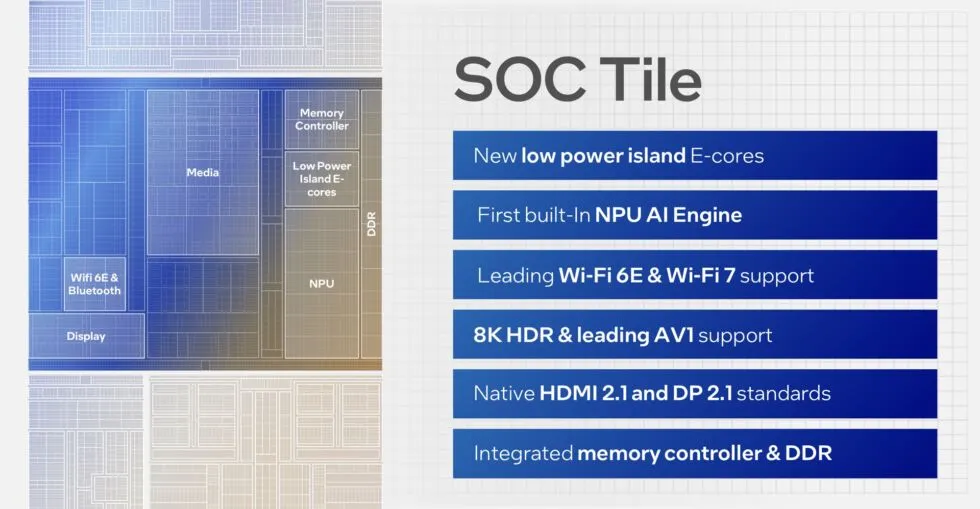

- SoC -flisen er nok den mest interessante af de fire. Det inkluderer to ekstra Crestmont E-kerner, mediekodnings- og afkodningsmotoren, der normalt ville være placeret i GPU’en, og den neurale behandlingsenhed (NPU), der bruges til at accelerere AI og maskinlærings-arbejdsbelastninger. Den håndterer også Wi-Fi og Bluetooth-forbindelse og tilslutning til eksterne skærme over HDMI 2.1 og DisplayPort 2.1.

En af de bemærkelsesværdige ting ved Meteor Lake er, at ikke alle fliserne bliver fremstillet af Intel. Computerflisen, som rummer de faktiske P-kerner og de fleste af E-kernerne, bruger den nye Intel 4-proces, en opgradering fra Intel 7-processen, der bruges til de fleste nuværende Core-chips. Men grafikflisen bliver lavet på en 5 nm TSMC-proces, mens IO-flisen og SoC-flisen er lavet på en 6 nm TSMC-proces.

Intel har også brugt TSMC’s fremstilling til at lave sine Arc GPU’er, så det er ikke første gang, vi har set disse to chipfremstillingsfrenemies arbejde sammen. Men Intel forsøger at indhente TSMC’s produktion, og Intel ser dets støberi som nøglen til dens fremtidige vækst. Jeg ville ikke blive overrasket, hvis det endelige mål er at flytte tilbage til alle Intel-fremstillede fliser.

Endnu flere E-kerner

Intel har sagt, at Meteor Lakes P-kerner ikke ændrer sig meget sammenlignet med dem, der bruges i 12. og 13. generation af Alder Lake og Raptor Lake CPU’er – vi kan se højere clockhastigheder, men ikke meget har ændret sig med hensyn til instruktioner – pr. ur eller instruktionssæt. E-kernerne får dog nogle forbedringer.

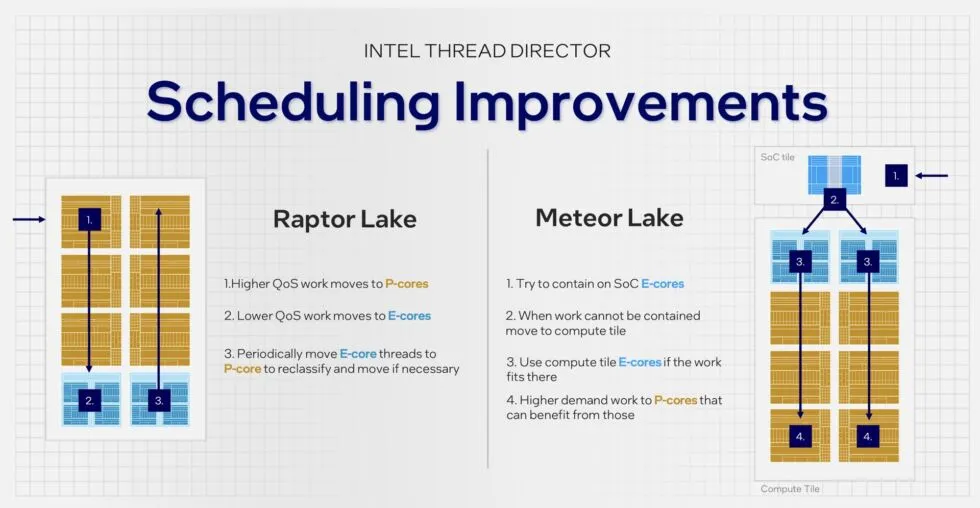

Meteor Lake omfatter faktisk to forskellige slags E-kerner. Der er to low-power (LP) E-kerner i SoC-flisen, og den opdaterede version af Intels Thread Director vil forsøge at bruge disse E-kerner til så mange opgaver som muligt. Intel kalder denne del af SoC-flisen for “low-power-øen”, fordi ideen er at tillade computerflisen og grafikflisen at slukke fuldstændigt så meget som muligt for at spare strøm.

Når opgaver kræver mere ydeevne, end LP E-kernerne kan levere, vil Thread Director sparke dem til computerflisen – enten til de vigtigste E-core-klynger, som er indstillet til at håndtere multitrådede arbejdsbelastninger med lav effekt, eller til P-kernerne , som bruges til enkelttrådede opgaver og ethvert flertrådsarbejde, E-kernerne ikke kan klare. Dette er en ændring fra, hvordan Thread Director fungerer i 12. og 13. generations processorer, hvor højt prioriterede opgaver ville gå direkte til P-kernerne uden at prøve E-kernerne først. (Selvom det stadig skal ses, om Thread Director-ændringerne vil resultere i nogen form for brugermærkbare forsinkelser for højtydende opgaver.)

Også værd at bemærke: Crestmont E-kerner kan tilføjes til processorer i grupper af to, hvor tidligere generation Gracement E-kerner kun kunne tilføjes i grupper af fire. Dette kan gøre det lettere for Intel at retfærdiggøre at bringe små grupper af E-kerner til processorer i lavere ende, som ikke havde dem før. Alle E-kerner forbliver enkeltgevindede, mens P-kerner stadig understøtter to gevind pr. kerne.

De nye E-kerner inkluderer også et par andre finesser – VNNI-instruktioner til at accelerere AI-arbejdsbelastninger og endda AVX10, som bringer mange af fordelene ved Intels AVX-512-instruktioner uden at kræve 512-bit registre. 12. og 13. generations Core-processorer lukkede fuldstændig AVX-512-understøttelse fra, fordi E-kernerne ikke understøttede det, selvom understøttelse var til stede i P-kernerne. Dette har skabt en akavet situation, hvor AMDs seneste Zen 4-chips understøtter AVX-512-instruktionerne, som Intel opfandt og promoverede, hvor Intels seneste forbrugerchips ikke gør det.

Skriv et svar