Intel, AMD und andere Schwergewichte der Branche schaffen einen neuen Chiplet-Standard

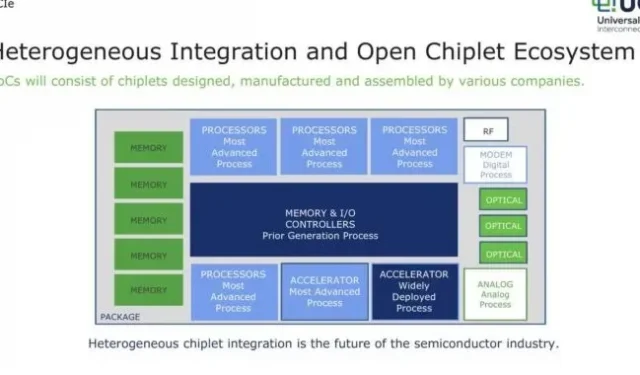

Einige der größten Prozessorhersteller, darunter Intel, AMD, Qualcomm, Arm, TSMC und Samsung, schließen sich zusammen, um einen neuen Standard für Chip-basierte Prozessoren zu definieren. Der neue Standard mit dem Namen Universal Chiplet Interconnect Express (kurz UCIe) zielt darauf ab, einen offenen, interoperablen Standard für die Kombination mehrerer Siliziumchips (oder Chiplets) in einem einzigen Gehäuse zu definieren.

Intel, AMD und andere entwickeln oder verkaufen bereits Chiplet-basierte Prozessoren in der einen oder anderen Form – die meisten AMD Ryzen-Prozessoren verwenden Chiplets, und zukünftige Intel Sapphire Rapids Xeon-Prozessoren werden dies auch tun. Aber alle diese Chips nutzen unterschiedliche Verbindungen, um die Kommunikation zwischen den Chiplets zu ermöglichen. Der UCIe-Standard wird sie, wenn er erfolgreich ist, durch einen einzigen Standard ersetzen, was es theoretisch für kleine Unternehmen einfacher macht, Chipsätze oder die Chips eines anderen Unternehmens in ihren eigenen Produkten zu verwenden.

Chipbasierte Designs sind für die Herstellung großer Chips an modernen Fertigungsstandorten von Vorteil, unter anderem weil sie die Menge an Silizium reduzieren, die Hersteller verschwenden müssen. Wenn ein Herstellungsfehler einen CPU-Kern betrifft, ist das Wegwerfen (oder Entfernen) eines 8-Kern-Chiplets viel billiger als das Wegwerfen eines riesigen 16- oder 32-Kern-CPU-Chips. Chipdesigns ermöglichen auch die Kombination von Chips und Herstellungsprozessen. Sie können beispielsweise einen älteren, günstigeren Prozess für Ihren Chipsatz und einen neueren, fortschrittlicheren Prozess für Prozessorkerne und Caches verwenden. Oder Sie können eine AMD-GPU im selben Gehäuse wie einen Intel-Prozessor unterbringen.

Laut AnandTech wird der UCIe-Standard die physikalischen und Protokollebenen des Chipdesigns abdecken. Der Standard definiert, wie Chiplets miteinander verbunden werden sollen, und legt ein Protokoll fest, um die Kommunikation zwischen Chiplets zu erleichtern. Den Chip-Designern steht es jedoch frei, diese Chiplets so zu verpacken, wie sie es für richtig halten, sodass die Chiplets direkt über das Gehäusesubstrat oder über eine siliziumbasierte Brücke oder einen anderen Vermittler miteinander kommunizieren können.

Um diesen unterschiedlichen physischen Verpackungsoptionen Rechnung zu tragen, definiert UCIe Version 1.0 zwei verschiedene Leistungsstufen. Das „Standard“-Paket erfordert 16 Datenspuren und bis zu 25 mm Abstand zwischen den Chipsätzen, während das „Extended“-Paket 64 Datenspuren verwendet und nur 2 mm Platz zulässt.

Die UCIe zugrunde liegenden Protokolle sind PCI Express und die zugehörigen Compute Express Link (CXL)-Standards, die den Chipherstellern wohlbekannt sind. Aber Unternehmen, die bereits fortschrittlichere oder dediziertere Protokolle für die Kommunikation zwischen Chipsätzen entwickelt haben, wie etwa AMD und sein Infinity Fabric , können diese Protokolle verwenden und gleichzeitig UCIe-konform bleiben. UCIe wurde ursprünglich von Intel entwickelt und dann an die breitere UCIe-Gruppe gespendet, um als Grundlage für einen neuen Standard zu dienen. Aber die Mitgliedsunternehmen der Gruppe werden noch in diesem Jahr „mit der Zusammenarbeit an der UCIe-Technologie der nächsten Generation beginnen“.

Wenn Sie weitere technische Details zum UCIe-Standard benötigen, finden Sie das Whitepaper hier .

Bilderliste von AMD

Schreibe einen Kommentar