Intel, AMD y otros pesos pesados de la industria están creando un nuevo estándar de chiplet

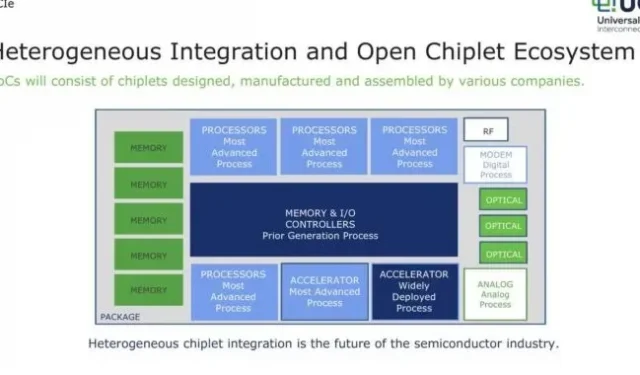

Algunos de los mayores fabricantes de procesadores, incluidos Intel, AMD, Qualcomm, Arm, TSMC y Samsung, se están uniendo para definir un nuevo estándar para los procesadores basados en chips. El nuevo estándar, llamado Universal Chiplet Interconnect Express (UCIe para abreviar), tiene como objetivo definir un estándar abierto e interoperable para combinar múltiples troqueles de silicio (o chiplets) en un solo paquete.

Intel, AMD y otros ya están desarrollando o vendiendo procesadores basados en chiplet de una forma u otra: la mayoría de los procesadores AMD Ryzen usan chiplets y los futuros procesadores Intel Sapphire Rapids Xeon también lo harán. Pero todos estos chips usan diferentes interconexiones para permitir la comunicación entre los chiplets. El estándar UCIe, si tiene éxito, los reemplazará con un único estándar, lo que en teoría facilitará que las pequeñas empresas utilicen conjuntos de chips o chips de otra empresa en sus propios productos.

Los diseños basados en chips son beneficiosos para la fabricación de chips grandes en sitios de fabricación avanzados, en parte porque reducen la cantidad de silicio que los fabricantes tienen que desperdiciar. Si un defecto de fabricación afecta a un núcleo de la CPU, desechar (o eliminar) un chiplet de 8 núcleos es mucho más económico que desechar una enorme matriz de CPU de 16 o 32 núcleos. Los diseños de chips también permiten la combinación de chips y procesos de fabricación. Por ejemplo, puede usar un proceso más antiguo y económico para su conjunto de chips y un proceso más nuevo y avanzado para los núcleos y cachés del procesador. O puede poner una GPU AMD en el mismo caso que un procesador Intel.

Según AnandTech , el estándar UCIe cubrirá las capas físicas y de protocolo del diseño de chips. El estándar definirá cómo se deben conectar los chiplets entre sí y un protocolo para facilitar la comunicación entre los chiplets. Pero los diseñadores de chips tendrán la libertad de empaquetar estos chips como mejor les parezca, permitiendo que los chips se comuniquen entre sí directamente a través del sustrato del paquete o utilizando algún tipo de puente basado en silicio u otro intermediario.

Para tener en cuenta estas diferentes opciones de empaquetado físico, la versión 1.0 de UCIe define dos niveles diferentes de rendimiento. El paquete «Estándar» requiere 16 líneas de datos y hasta 25 mm de espacio entre conjuntos de chips, mientras que el paquete «Extendido» usa 64 líneas de datos y solo permite un espacio de 2 mm.

Los protocolos subyacentes de UCIe son PCI Express y los estándares Compute Express Link (CXL) relacionados, que son bien conocidos por los fabricantes de chips. Pero las empresas que ya han desarrollado protocolos más avanzados o dedicados para la comunicación entre conjuntos de chips, como AMD y su Infinity Fabric , podrán usar estos protocolos sin dejar de cumplir con UCIe. UCIe fue desarrollado originalmente por Intel y luego donado al grupo UCIe más amplio para que sirviera como base para un nuevo estándar. Pero las compañías miembro del grupo “comenzarán a trabajar juntas en la tecnología UCIe de próxima generación” a partir de finales de este año.

Si necesita más detalles técnicos sobre el estándar UCIe, puede encontrar el documento técnico aquí .

Listado de imágenes de AMD

Deja una respuesta