Intel, AMD et d’autres poids lourds de l’industrie créent une nouvelle norme de puces

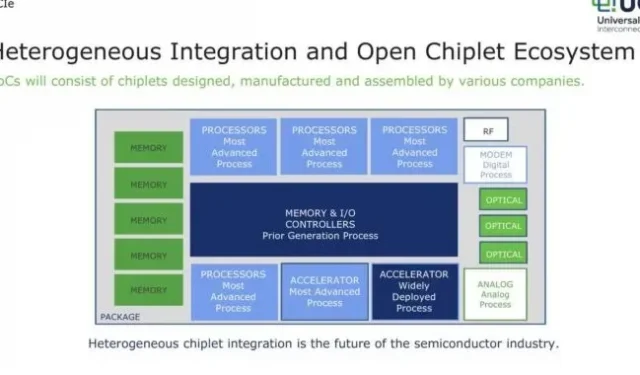

Certains des plus grands fabricants de processeurs, dont Intel, AMD, Qualcomm, Arm, TSMC et Samsung, s’associent pour définir une nouvelle norme pour les processeurs à puce. La nouvelle norme, appelée Universal Chiplet Interconnect Express (UCIe en abrégé), vise à définir une norme ouverte et interopérable pour combiner plusieurs puces en silicium (ou puces) en un seul boîtier.

Intel, AMD et d’autres développent ou vendent déjà des processeurs basés sur des chiplets sous une forme ou une autre – la plupart des processeurs AMD Ryzen utilisent des chiplets, et les futurs processeurs Intel Sapphire Rapids Xeon le feront également. Mais toutes ces puces utilisent des interconnexions différentes pour permettre la communication entre les puces. La norme UCIe, si elle réussit, les remplacera par une norme unique, permettant théoriquement aux petites entreprises d’utiliser plus facilement des chipsets ou d’utiliser les puces d’une autre entreprise dans leurs propres produits.

Les conceptions à base de puces sont avantageuses pour la fabrication de grandes puces sur des sites de fabrication avancés, en partie parce qu’elles réduisent la quantité de silicium que les fabricants doivent gaspiller. Si un défaut de fabrication affecte un cœur de processeur, jeter (ou supprimer) un chiplet à 8 cœurs est beaucoup moins cher que de jeter un énorme dé de processeur à 16 ou 32 cœurs. Les conceptions de puces permettent également la combinaison de puces et de processus de fabrication. Par exemple, vous pouvez utiliser un processus plus ancien et moins cher pour votre chipset et un processus plus récent et plus avancé pour les cœurs de processeur et les caches. Ou vous pouvez mettre un GPU AMD dans le même boîtier qu’un processeur Intel.

Selon AnandTech , la norme UCIe couvrira les couches physique et protocolaire de la conception des puces. La norme définira comment les chiplets doivent être connectés les uns aux autres et un protocole pour faciliter la communication entre les chiplets. Mais les concepteurs de puces seront libres de conditionner ces puces comme bon leur semble, permettant aux puces de communiquer entre elles directement via le substrat du boîtier ou en utilisant une sorte de pont à base de silicium ou un autre intermédiaire.

Pour tenir compte de ces différentes options d’emballage physique, la version UCIe 1.0 définit deux niveaux de performance différents. Le package « Standard » nécessite 16 voies de données et jusqu’à 25 mm d’espace entre les chipsets, tandis que le package « Extended » utilise 64 voies de données et n’autorise qu’un espace de 2 mm.

Les protocoles sous-jacents à UCIe sont PCI Express et les normes Compute Express Link (CXL) associées, qui sont bien connues des fabricants de puces. Mais les entreprises qui ont déjà développé des protocoles plus avancés ou dédiés pour la communication entre les chipsets, comme AMD et son Infinity Fabric , pourront utiliser ces protocoles tout en restant conformes à l’UCIe. UCIe a été initialement développé par Intel, puis donné au groupe UCIe plus large pour servir de base à une nouvelle norme. Mais les sociétés membres du groupe « commenceront à travailler ensemble sur la technologie UCIe de nouvelle génération » à partir de la fin de cette année.

Si vous avez besoin de plus de détails techniques sur la norme UCIe, vous pouvez trouver le livre blanc ici .

Liste d’images d’ AMD

Laisser un commentaire