Intel, AMD e altri pesi massimi del settore stanno creando un nuovo standard per i chiplet

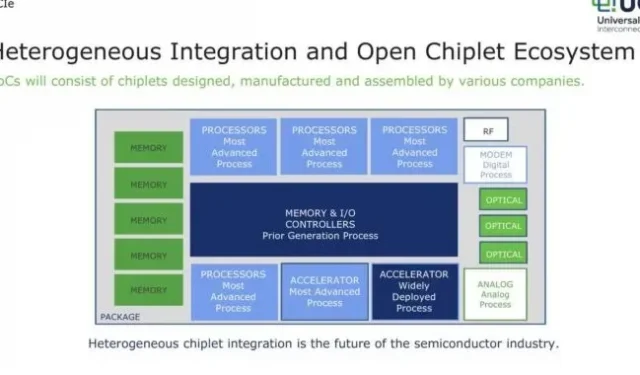

Alcuni dei maggiori produttori di processori, tra cui Intel, AMD, Qualcomm, Arm, TSMC e Samsung, stanno collaborando per definire un nuovo standard per i processori basati su chip. Il nuovo standard, chiamato Universal Chiplet Interconnect Express (in breve UCIe), mira a definire uno standard aperto e interoperabile per combinare più die in silicio (o chiplet) in un unico pacchetto.

Intel, AMD e altri stanno già sviluppando o vendendo processori basati su chiplet in una forma o nell’altra: la maggior parte dei processori AMD Ryzen utilizza chiplet e anche i futuri processori Intel Sapphire Rapids Xeon lo faranno. Ma tutti questi chip utilizzano interconnessioni diverse per consentire la comunicazione tra i chiplet. Lo standard UCIe, se avrà successo, li sostituirà con un unico standard, rendendo teoricamente più facile per le piccole aziende utilizzare chipset o utilizzare i chip di un’altra azienda nei propri prodotti.

I progetti basati su chip sono vantaggiosi per la fabbricazione di chip di grandi dimensioni nei siti di produzione avanzati, in parte perché riducono la quantità di silicio che i produttori devono sprecare. Se un difetto di fabbricazione interessa un core della CPU, buttare via (o rimuovere) un chiplet a 8 core è molto più economico che buttare via un enorme die della CPU a 16 o 32 core. I progetti di chip consentono anche la combinazione di chip e processi di produzione. Ad esempio, puoi utilizzare un processo più vecchio ed economico per il tuo chipset e un processo più nuovo e più avanzato per i core del processore e le cache. Oppure puoi inserire una GPU AMD nello stesso case di un processore Intel.

Secondo AnandTech , lo standard UCIe coprirà i livelli fisici e di protocollo della progettazione dei chip. Lo standard definirà come i chiplet dovrebbero essere collegati tra loro e un protocollo per facilitare la comunicazione tra chiplet. Ma i progettisti di chip saranno liberi di impacchettare questi chiplet nel modo che ritengono opportuno, consentendo ai chiplet di comunicare tra loro direttamente attraverso il substrato del pacchetto o utilizzando una sorta di bridge a base di silicio o altro intermediario.

Per tenere conto di queste diverse opzioni di confezionamento fisico, UCIe versione 1.0 definisce due diversi livelli di prestazioni. Il pacchetto “Standard” richiede 16 corsie dati e fino a 25 mm di spazio tra i chipset, mentre il pacchetto “Esteso” utilizza 64 corsie dati e consente solo 2 mm di spazio.

I protocolli alla base di UCIe sono PCI Express e i relativi standard Compute Express Link (CXL), ben noti ai produttori di chip. Ma le aziende che hanno già sviluppato protocolli più avanzati o dedicati per la comunicazione tra chipset, come AMD e il suo Infinity Fabric , potranno utilizzare questi protocolli pur rimanendo conformi a UCIe. UCIe è stato originariamente sviluppato da Intel e poi donato al più ampio gruppo UCIe per fungere da base per un nuovo standard. Ma le società che fanno parte del gruppo “inizieranno a lavorare insieme sulla tecnologia UCIe di prossima generazione” a partire dalla fine dell’anno.

Se hai bisogno di maggiori dettagli tecnici sullo standard UCIe, puoi trovare il white paper qui .

Elenco di immagini da AMD

Lascia un commento