Intel、AMD、その他の業界の有力企業が新しいチップレット標準を作成しています

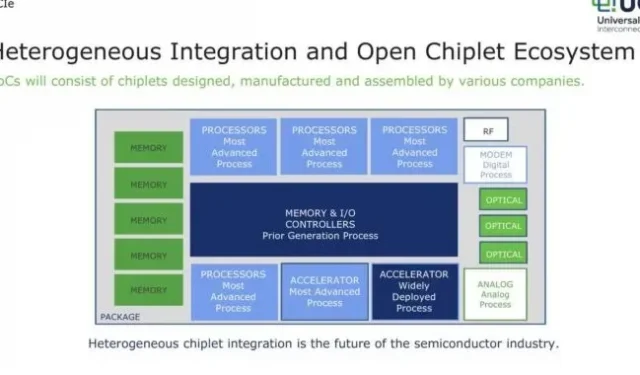

Intel、AMD、Qualcomm、Arm、TSMC、Samsung などの大手プロセッサ メーカーの一部が、チップベースのプロセッサの新しい標準を定義するために協力しています。Universal Chiplet Interconnect Express (略して UCIe) と呼ばれるこの新しい標準は 、複数のシリコン ダイ (またはチップレット) を 1 つのパッケージに組み合わせるためのオープンで相互運用可能な標準を定義することを目的としています。

Intel、AMD、その他の企業は、すでに何らかの形でチップレットベースのプロセッサを開発または販売しています。ほとんどの AMD Ryzen プロセッサはチップレットを使用しており、将来の Intel Sapphire Rapids Xeon プロセッサも使用する予定です。ただし、これらのチップはすべて、チップレット間の通信を可能にするために異なる相互接続を使用します。UCIe規格が成功すれば、それらは単一規格に置き換わることになり、理論的には小規模企業がチップセットを使用したり、他社のチップを自社製品に使用したりすることが容易になる。

チップベースの設計は、メーカーが無駄にするシリコンの量を削減できるため、先進的な製造現場での大規模チップの製造に有益です。製造上の欠陥が 1 つの CPU コアに影響を及ぼした場合、1 つの 8 コア チップレットを廃棄 (または削除) する方が、16 コアまたは 32 コアの巨大な CPU ダイを廃棄するよりもはるかに安価です。チップ設計により、チップと製造プロセスの組み合わせも可能になります。たとえば、チップセットには古い安価なプロセスを使用し、プロセッサ コアとキャッシュには新しいより高度なプロセスを使用できます。または、AMD GPU を Intel プロセッサと同じケースに入れることもできます。

AnandTechによると、UCIe 標準はチップ設計の物理層とプロトコル層をカバーする予定です。この規格では、チップレットを相互に接続する方法と、チップレット間の通信を容易にするプロトコルを定義します。しかし、チップ設計者は、適切と思われる方法でこれらのチップレットを自由にパッケージ化することができ、チップレットがパッケージ基板を介して直接、あるいはある種のシリコンベースのブリッジやその他の仲介手段を使用して相互に通信できるようになります。

これらのさまざまな物理パッケージング オプションを考慮して、UCIe バージョン 1.0 では 2 つの異なるパフォーマンス レベルが定義されています。「標準」パッケージは 16 個のデータ レーンとチップセット間の最大 25mm のスペースを必要としますが、「拡張」パッケージは 64 個のデータ レーンを使用し、2mm のスペースしか許可されません。

UCIe の基礎となるプロトコルは、チップ メーカーにはよく知られている PCI Express および関連する Compute Express Link (CXL) 標準です。ただし、AMD とその Infinity Fabricなど、チップセット間の通信のためのより高度なプロトコルまたは専用プロトコルをすでに開発している企業は、UCIe 準拠を維持しながらこれらのプロトコルを使用できます。UCIe はもともとインテルによって開発され、その後新しい標準の基礎として機能するためにより広範な UCIe グループに寄贈されました。しかし、グループのメンバー企業は今年後半から「次世代のUCIeテクノロジーに協力し始める」予定だ。

UCIe 標準に関する技術的な詳細が必要な場合は、ここでホワイト ペーパーを見つけることができます。

AMDからのイメージリスト

コメントを残す