インテルのここ数年で最大のラップトップ CPU アップデートは過去の設計から大きく脱却

Intel の次世代 Meteor Lake ラップトップ プロセッサの発売が近づいています。同社は今週、最初のプロセッサが 12 月 14 日に発売されると発表しました。実際の Core および Core Ultra システムがその日に購入できるかどうかは不明ですが、少なくとも、この公式発表は、1月のCESでの多くのラップトップ発表への道を開くことになります。

私たちはすでに Meteor Lake について多くの基本的な事実を知っています。単一のモノリシック ダイではなく、Intel と TSMC の両方が製造したチップレットを組み合わせて使用しており、 Intel の「第 n 世代」および i3/i5/i7/i9 ブランドの廃止を意味します。また、デスクトップ向けにはまだ準備ができておらず、次期 Core デスクトップ CPU は第 12 世代および第 13 世代のチップと非常に似たものになることもわかっています。

しかし、今週開催されたIntelのイノベーションイベントでは、同社はMeteor Lakeの進歩の一部をもう少し深く掘り下げ、チップがEコアとPコアのバランスをどのようにとるかについてさらに説明し、ここ数年で最も大幅な統合GPUアップグレードを発表した。以下にハイライトをいくつか紹介しますが、詳細については、プレゼンテーション全体を視聴または読む価値があります。

数マイル分のタイル

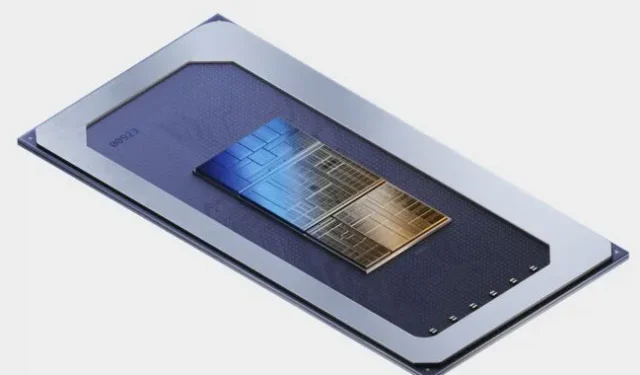

Meteor Lake は、チップレット ベースの設計に移行した Intel の最初のコンシューマ プロセッサになります。CPU、GPU、および最新のラップトップ CPU に必要なその他すべての要素を含む 1 つのモノリシック ダイではなく、Meteor Lake は 4 つに分割されています。 5 番目の基本タイルによって結合され、相互に通信できるようにする「タイル」。ベース タイルの上にチップレットを積み重ねるプロセスは、Intel がFoverosと呼ぶパッケージング テクノロジです。

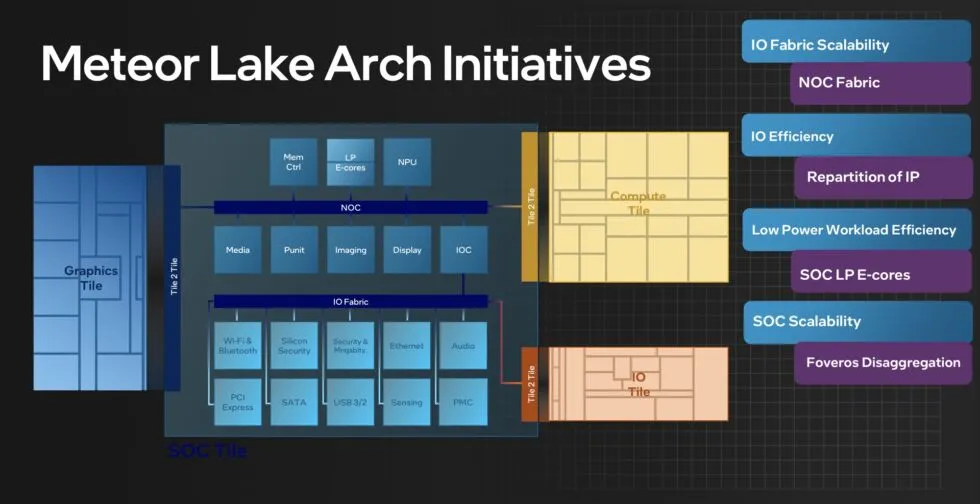

これら 4 つのタイルのそれぞれに含まれる内容の基本的な内訳は次のとおりです。

- コンピューティング タイルには、実際の CPU の大部分が配置されます。Intel の現在のレンダリングでは、Redwood Cove アーキテクチャに基づいた 6 つの高性能 P コアと、Crestmont アーキテクチャに基づいた 8 つの高効率 E コアを備えたチップが示されています。

- グラフィックス タイルはほとんどのグラフィックス処理が行われる場所ですが、通常 GPU にあるいくつかの特定の機能は他のタイルに移動されています。Meteor Lake の統合 GPU は、ほとんどが Intel Arc 専用 GPU の統合バージョンであり、ハードウェア レイ トレーシング アクセラレーションを備えています。

- IOタイルは、 PCI Express 5.0 レーンや Thunderbolt 4 のサポートなど、ほとんどの外部接続を処理します ( Thunderbolt 5は待つ必要があります)。

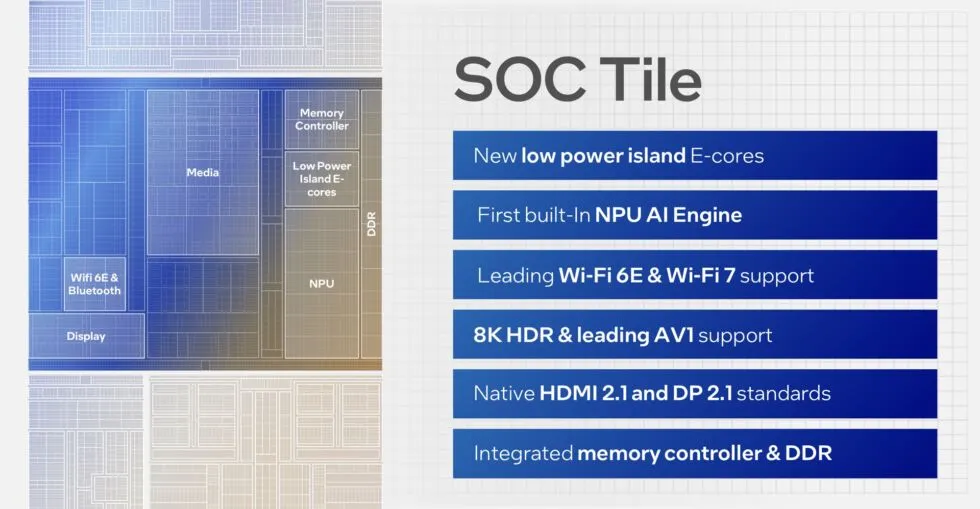

- SoC タイルは、おそらく4 つの中で最も興味深いものです。これには、2 つの追加の Crestmont E コア、通常 GPU に配置されるメディア エンコードおよびデコード エンジン、AI および機械学習ワークロードの高速化に使用されるニューラル プロセッシング ユニット (NPU) が含まれています。また、Wi-Fi および Bluetooth 接続、HDMI 2.1 および DisplayPort 2.1 経由の外部ディスプレイへの接続も処理します。

Meteor Lake で注目すべき点の 1 つは、すべてのタイルが Intel によって製造されているわけではないことです。実際の P コアとほとんどの E コアを収容するコンピューティング タイルは、最新の Core チップに使用されている Intel 7 プロセスからのアップグレードである新しい Intel 4 プロセスを使用します。ただし、グラフィックス タイルは 5 nm TSMC プロセスで製造されており、IO タイルと SoC タイルは 6 nm TSMC プロセスで製造されています。

Intel も TSMC の製造技術を利用して Arc GPU を製造しているため、この 2 つのチップ製造の敵対関係が連携するのを見るのはこれが初めてではありません。しかしインテルはTSMCの製造業に追いつこうとしており、インテルは自社のファウンドリ事業が将来の成長の鍵となると考えている。すべてインテル製のタイルに戻すことが最終的な目標であっても、私は驚かないでしょう。

さらに多くの E コア

Intel は、Meteor Lake の P コアは、第 12 世代および第 13 世代の Alder Lake および Raptor Lake CPU で使用されているものと大きな変化はないと述べています。クロック速度は向上する可能性がありますが、命令の点では大きな変化はありません。クロックまたは命令セットごとに。ただし、E コアにはいくつかの改善が施されています。

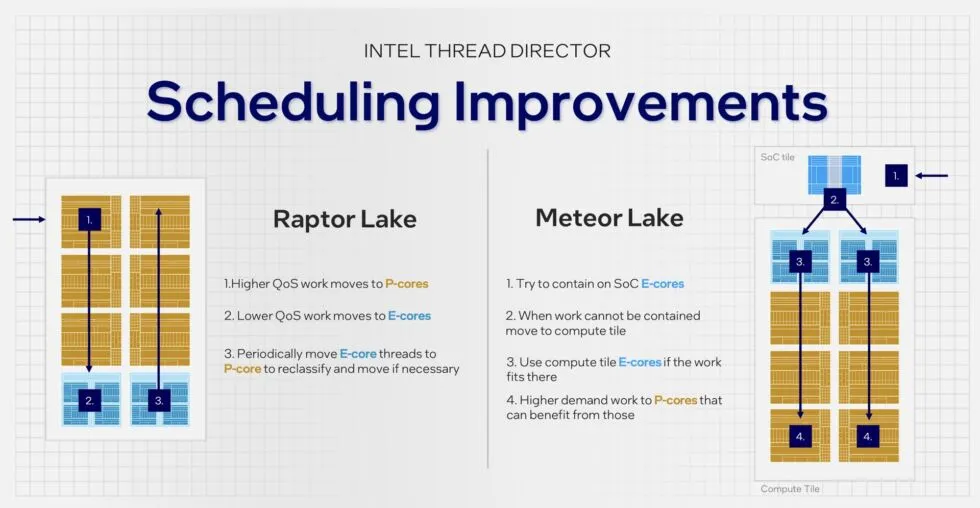

Meteor Lake には実際には 2 種類の E コアが含まれています。SoC タイルには 2 つの低電力 (LP) E コアがあり、Intel の Thread Director の更新バージョンは、これらの E コアを可能な限り多くのタスクに使用しようとします。Intel は、SoC タイルのこの部分を「低電力アイランド」と呼んでいます。これは、電力を節約するために、コンピューティング タイルとグラフィックス タイルの電力を可能な限り完全にオフにすることが考えられているためです。

タスクが LP E コアが提供できる以上のパフォーマンスを必要とする場合、Thread Director はタスクをコンピューティング タイル (影響の少ないマルチスレッド ワークロードを処理するように調整されたメイン E コア クラスター、または P コアのいずれか) に割り当てます。 、シングル スレッド タスクおよび E コアが処理できないマルチスレッド作業に使用されます。これは、優先度の高いタスクが最初に E コアを試行せずに P コアに直接向かう、第 12 世代および第 13 世代プロセッサでの Thread Director の動作方法からの変更です。(ただし、スレッド ディレクタの変更によって、高パフォーマンスのタスクにユーザーが気づくような遅延が発生するかどうかはまだわかりません。)

また、注目に値します。Crestmont E コアは 2 つのグループでプロセッサに追加できますが、前世代の Gracement E コアは 4 つのグループでしか追加できませんでした。これにより、Intel は、これまで E コアを搭載していなかったローエンド プロセッサに小さなグループの E コアを導入することを正当化することが容易になる可能性があります。すべての E コアはシングルスレッドのままですが、P コアは引き続きコアあたり 2 つのスレッドをサポートします。

新しい E コアには、 AI ワークロードを高速化するためのVNNI 命令や、 512 ビット レジスタを必要とせずにインテルの AVX-512 命令の利点の多くをもたらす AVX10 など、その他の優れた点もいくつか含まれています。第 12 世代と第 13 世代の Core プロセッサでは、AVX-512 のサポートが完全に停止されました。これは、P コアではサポートが存在していても、E コアでは AVX-512 がサポートされていなかったためです。これにより、AMD の最新の Zen 4 チップは、Intel が発明し推進した AVX-512 命令をサポートしているのに、Intel の最新のコンシューマー向けチップはサポートしていないという厄介な状況が生じています。

コメントを残す