인텔, AMD 및 기타 업계 거물급 기업들이 새로운 칩렛 표준을 만들고 있습니다.

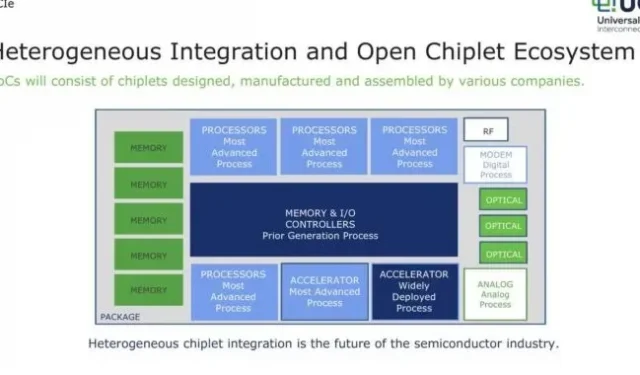

Intel, AMD, Qualcomm, Arm, TSMC 및 Samsung을 포함한 일부 최대 프로세서 제조업체는 팀을 구성하여 칩 기반 프로세서의 새로운 표준을 정의하고 있습니다. UCIe( Universal Chiplet Interconnect Express ) 라고 하는 새로운 표준은 여러 실리콘 다이(또는 칩렛)를 단일 패키지로 결합하기 위한 개방형 상호 운용 표준을 정의하는 것을 목표로 합니다.

Intel, AMD 등은 이미 어떤 형태로든 칩렛 기반 프로세서를 개발하거나 판매하고 있습니다. 대부분의 AMD Ryzen 프로세서는 칩렛을 사용하며 향후 Intel Sapphire Rapids Xeon 프로세서도 그렇게 할 것입니다. 그러나 이러한 모든 칩은 서로 다른 상호 연결을 사용하여 칩렛 간의 통신을 가능하게 합니다. UCIe 표준이 성공하면 단일 표준으로 대체되어 이론적으로 소기업이 칩셋을 사용하거나 자체 제품에 다른 회사의 칩을 사용하는 것이 더 쉬워집니다.

칩 기반 설계는 부분적으로 제조업체가 낭비해야 하는 실리콘의 양을 줄이기 때문에 고급 제조 현장에서 대형 칩 제조에 유리합니다. 제조 결함이 하나의 CPU 코어에 영향을 미치는 경우 하나의 8코어 칩렛을 버리는(또는 제거하는) 것이 거대한 16코어 또는 32코어 CPU 다이를 버리는 것보다 훨씬 저렴합니다. 칩 설계는 또한 칩과 제조 공정의 조합을 허용합니다. 예를 들어 칩셋에는 더 오래되고 저렴한 프로세스를 사용하고 프로세서 코어 및 캐시에는 더 새롭고 고급 프로세스를 사용할 수 있습니다. 또는 Intel 프로세서와 동일한 케이스에 AMD GPU를 넣을 수 있습니다.

AnandTech 에 따르면 UCIe 표준은 칩 설계의 물리적 및 프로토콜 계층을 다룰 것입니다. 이 표준은 칩렛이 서로 연결되는 방법과 칩렛 간의 통신을 용이하게 하는 프로토콜을 정의합니다. 그러나 칩 설계자는 이러한 칩렛을 자유롭게 패키징할 수 있지만 적합하다고 판단되면 칩렛이 패키지 기판을 통해 직접 또는 일종의 실리콘 기반 브리지 또는 기타 매개체를 사용하여 서로 통신할 수 있습니다.

이러한 다양한 물리적 패키징 옵션을 설명하기 위해 UCIe 버전 1.0은 두 가지 성능 수준을 정의합니다. “Standard” 패키지는 16개의 데이터 레인과 칩셋 사이에 최대 25mm의 공간이 필요한 반면, “Extended” 패키지는 64개의 데이터 레인을 사용하고 2mm의 공간만 허용합니다.

UCIe의 기반이 되는 프로토콜은 칩 제조업체에게 잘 알려진 PCI Express 및 관련 CXL(Compute Express Link) 표준입니다. 그러나 AMD와 Infinity Fabric 과 같이 칩셋 간의 통신을 위해 이미 고급 또는 전용 프로토콜을 개발한 회사는 UCIe 규격을 유지하면서 이러한 프로토콜을 사용할 수 있습니다. UCIe는 원래 인텔에서 개발한 후 더 넓은 UCIe 그룹에 기부되어 새로운 표준의 기반이 되었습니다. 그러나 이 그룹의 회원사들은 올해 말부터 “차세대 UCIe 기술에 대한 협력을 시작할 것”입니다.

UCIe 표준에 대한 자세한 기술 정보가 필요한 경우 여기에서 백서를 찾을 수 있습니다 .

AMD 의 이미지 목록

답글 남기기