„Intel“, AMD ir kiti pramonės sunkiasvoriai kuria naują mikroschemų standartą

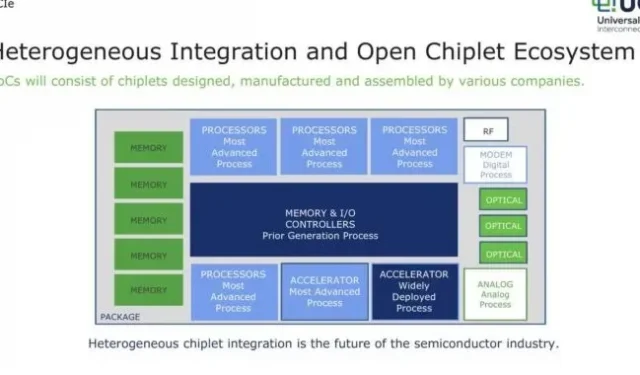

Kai kurie didžiausi procesorių gamintojai, įskaitant „Intel“, AMD, „Qualcomm“, „Arm“, TSMC ir „Samsung“, bendradarbiauja, kad nustatytų naują lustų procesorių standartą. Naujasis standartas, vadinamas Universal Chiplet Interconnect Express (sutrumpintai UCIe), siekia apibrėžti atvirą, sąveikų standartą, leidžiantį sujungti kelis silicio štampelius (arba mikroschemas) į vieną paketą.

„Intel“, „AMD“ ir kiti jau kuria arba parduoda vienokia ar kitokia lustų pagrindu veikiančius procesorius – dauguma „AMD Ryzen“ procesorių naudoja mikroschemas, o būsimi „Intel Sapphire Rapids Xeon“ procesoriai taip pat. Tačiau visi šie lustai naudoja skirtingas jungtis, kad būtų galima bendrauti tarp mikroschemų. UCIe standartas, jei pasiseks, pakeis juos vienu standartu, teoriškai leisdamas mažoms įmonėms lengviau naudoti mikroschemų rinkinius arba naudoti kitos įmonės lustus savo gaminiuose.

Lustų dizainas yra naudingas didelių lustų gamybai pažangiose gamybos vietose, iš dalies dėl to, kad jie sumažina silicio, kurį gamintojai turi eikvoti, kiekį. Jei gamybos defektas paveikia vieną procesoriaus branduolį, vieną 8 branduolių mikroschemą išmesti (arba pašalinti) yra daug pigiau, nei išmesti didžiulį 16 ar 32 branduolių procesoriaus bloką. Lustų dizainas taip pat leidžia derinti lustus ir gamybos procesus. Pavyzdžiui, savo lustų rinkiniui galite naudoti senesnį, pigesnį procesą, o procesoriaus branduoliams ir talpykloms – naujesnį, pažangesnį procesą. Arba galite įdėti AMD GPU į tą patį dėklą kaip „Intel” procesorių.

„AnandTech“ teigimu , UCIe standartas apims fizinį ir protokolinį lusto dizaino sluoksnius. Standarte bus apibrėžta, kaip mikroschemos turi būti sujungtos viena su kita, ir protokolas, palengvinantis ryšį tarp mikroschemų. Tačiau lustų dizaineriai galės laisvai supakuoti šias mikroschemas, kaip jiems atrodo tinkama, leisdami lustams susisiekti tarpusavyje tiesiogiai per pakuotės pagrindą arba naudodami kokį nors silicio pagrindo tiltelį ar kitą tarpininką.

Siekiant atsižvelgti į šias skirtingas fizinio pakavimo parinktis, UCIe 1.0 versija apibrėžia du skirtingus našumo lygius. „Standartiniam“ paketui reikia 16 duomenų juostų ir iki 25 mm tarpo tarp mikroschemų rinkinių, o „Extended“ paketui naudojamos 64 duomenų juostos ir leidžia tik 2 mm vietos.

Protokolai, kuriais grindžiamas UCIe, yra PCI Express ir susiję Compute Express Link (CXL) standartai, kurie yra gerai žinomi lustų gamintojams. Tačiau įmonės, kurios jau yra sukūrusios pažangesnius arba specialius ryšio tarp mikroschemų rinkinių protokolus, pvz., AMD ir jo Infinity Fabric , galės naudoti šiuos protokolus, likdamos suderinamos su UCIe. UCIe iš pradžių sukūrė „Intel“, o vėliau paaukojo platesnei UCIe grupei, kad ji būtų naujo standarto pagrindas. Tačiau grupės įmonės narės „pradės kartu dirbti su naujos kartos UCIe technologija“ nuo šių metų vėliau.

Jei jums reikia daugiau techninės informacijos apie UCIe standartą, baltą knygą galite rasti čia .

Vaizdų sąrašas iš AMD

Parašykite komentarą