Intel, AMD un citi nozares smagsvari veido jaunu mikroshēmu standartu

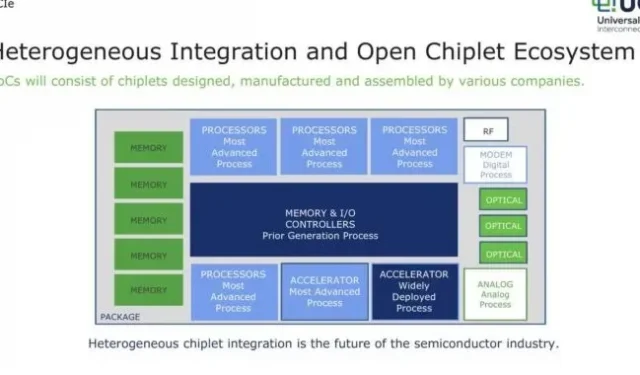

Daži no lielākajiem procesoru ražotājiem, tostarp Intel, AMD, Qualcomm, Arm, TSMC un Samsung, sadarbojas, lai definētu jaunu standartu procesoriem, kuru pamatā ir mikroshēmas. Jaunā standarta, ko sauc par Universal Chiplet Interconnect Express (īsumā UCIe), mērķis ir definēt atvērtu, sadarbspējīgu standartu vairāku silīcija presformu (vai mikroshēmu) apvienošanai vienā iepakojumā.

Intel, AMD un citi jau izstrādā vai pārdod uz mikroshēmām balstītus procesorus vienā vai otrā veidā — lielākā daļa AMD Ryzen procesoru izmanto mikroshēmas, un to darīs arī nākamie Intel Sapphire Rapids Xeon procesori. Bet visas šīs mikroshēmas izmanto dažādus starpsavienojumus, lai nodrošinātu saziņu starp mikroshēmām. UCIe standarts, ja tas izdosies, tos aizstās ar vienotu standartu, teorētiski atvieglojot mazajiem uzņēmumiem mikroshēmu izmantošanu vai cita uzņēmuma mikroshēmu izmantošanu savos produktos.

Uz mikroshēmām balstīti dizaini ir izdevīgi lielu mikroshēmu ražošanai progresīvās ražošanas vietās, daļēji tāpēc, ka tie samazina silīcija daudzumu, kas ražotājiem ir jātērē. Ja ražošanas defekts ietekmē vienu CPU kodolu, izmest (vai noņemt) vienu 8 kodolu mikroshēmu ir daudz lētāk nekā izmest milzīgu 16 vai 32 kodolu CPU uzgali. Mikroshēmu dizains arī ļauj kombinēt mikroshēmas un ražošanas procesus. Piemēram, varat izmantot vecāku, lētāku procesu savam mikroshēmojumam un jaunāku, progresīvāku procesu procesora kodoliem un kešatmiņām. Vai arī varat ievietot AMD GPU vienā korpusā ar Intel procesoru.

Saskaņā ar AnandTech , UCIe standarts aptvers mikroshēmu dizaina fiziskos un protokola slāņus. Standarts noteiks, kā mikroshēmām jābūt savienotām viena ar otru, un protokolu, lai atvieglotu saziņu starp mikroshēmām. Bet mikroshēmu izstrādātāji varēs brīvi iepakot šīs mikroshēmas, kā viņi uzskata par piemērotu, ļaujot mikroshēmām sazināties savā starpā tieši caur iepakojuma substrātu vai izmantojot kādu silīcija bāzes tiltu vai citu starpnieku.

Lai ņemtu vērā šīs dažādās fiziskās iepakojuma iespējas, UCIe versija 1.0 definē divus dažādus veiktspējas līmeņus. “Standarta” pakotnei ir nepieciešamas 16 datu joslas un līdz 25 mm atstarpe starp mikroshēmojumiem, savukārt “Extended” pakotnei tiek izmantotas 64 datu joslas un ir atļauta tikai 2 mm vieta.

UCIe pamatā esošie protokoli ir PCI Express un saistītie Compute Express Link (CXL) standarti, kas ir labi zināmi mikroshēmu ražotājiem. Taču uzņēmumi, kas jau ir izstrādājuši progresīvākus vai specializētākus protokolus saziņai starp mikroshēmojumiem, piemēram, AMD un tā Infinity Fabric , varēs izmantot šos protokolus, vienlaikus saglabājot UCIe saderību. UCIe sākotnēji izstrādāja Intel un pēc tam ziedoja plašākai UCIe grupai, lai kalpotu par pamatu jaunam standartam. Taču grupas dalībuzņēmumi “sāks strādāt kopā pie nākamās paaudzes UCIe tehnoloģijas”, sākot ar šī gada beigām.

Ja jums nepieciešama papildu tehniska informācija par UCIe standartu, balto papīru varat atrast šeit .

Attēlu saraksts no AMD

Atbildēt