Intel, AMD en andere zwaargewichten in de industrie creëren een nieuwe chipletstandaard

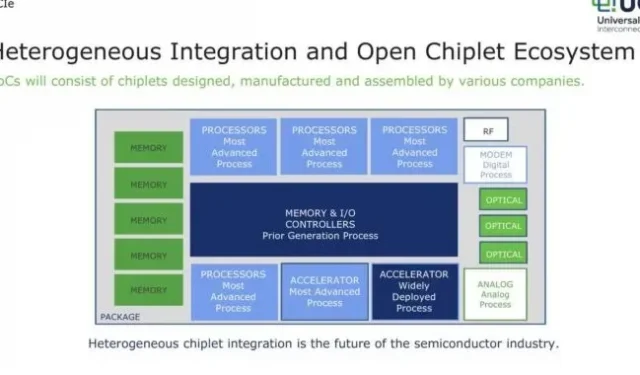

Enkele van de grootste processorfabrikanten, waaronder Intel, AMD, Qualcomm, Arm, TSMC en Samsung, werken samen om een nieuwe standaard voor chipgebaseerde processors te definiëren. De nieuwe standaard, genaamd Universal Chiplet Interconnect Express (afgekort UCIe), heeft tot doel een open, interoperabele standaard te definiëren voor het combineren van meerdere siliciumchips (of chiplets) in één pakket.

Intel, AMD en anderen ontwikkelen of verkopen al chiplet-gebaseerde processors in een of andere vorm – de meeste AMD Ryzen-processors gebruiken chiplets, en toekomstige Intel Sapphire Rapids Xeon-processors zullen dat ook doen. Maar al deze chips gebruiken verschillende interconnects om communicatie tussen de chiplets mogelijk te maken. Als de UCIe-standaard slaagt, zal deze worden vervangen door een enkele standaard, waardoor het in theorie gemakkelijker wordt voor kleine bedrijven om chipsets te gebruiken of de chips van een ander bedrijf in hun eigen producten te gebruiken.

Op chips gebaseerde ontwerpen zijn gunstig voor de fabricage van grote chips op geavanceerde productielocaties, deels omdat ze de hoeveelheid silicium verminderen die fabrikanten moeten verspillen. Als een fabricagefout één CPU-kern treft, is het weggooien (of verwijderen) van één 8-core chiplet veel goedkoper dan het weggooien van een enorme 16- of 32-core CPU-chip. Chipontwerpen maken ook de combinatie van chips en fabricageprocessen mogelijk. U kunt bijvoorbeeld een ouder, goedkoper proces gebruiken voor uw chipset en een nieuwer, geavanceerder proces voor processorcores en caches. Of je stopt een AMD GPU in dezelfde behuizing als een Intel processor.

Volgens AnandTech zal de UCIe-standaard de fysieke en protocollagen van het chipontwerp dekken. De standaard zal definiëren hoe chiplets met elkaar moeten worden verbonden en een protocol om de communicatie tussen chiplets te vergemakkelijken. Maar chipontwerpers zullen vrij zijn om deze chiplets naar eigen goeddunken te verpakken, waardoor de chiplets rechtstreeks met elkaar kunnen communiceren via het pakketsubstraat of met behulp van een soort op silicium gebaseerde brug of een andere tussenpersoon.

Om rekening te houden met deze verschillende fysieke verpakkingsopties, definieert UCIe versie 1.0 twee verschillende prestatieniveaus. Het “Standaard” -pakket vereist 16 datalijnen en tot 25 mm ruimte tussen chipsets, terwijl het “Uitgebreide” pakket 64 gegevenslijnen gebruikt en slechts 2 mm ruimte toestaat.

De protocollen die ten grondslag liggen aan UCIe zijn PCI Express en de gerelateerde Compute Express Link (CXL)-standaarden, die bekend zijn bij chipfabrikanten. Maar bedrijven die al meer geavanceerde of speciale protocollen hebben ontwikkeld voor communicatie tussen chipsets, zoals AMD en zijn Infinity Fabric , zullen deze protocollen kunnen gebruiken terwijl ze UCIe-compatibel blijven. UCIe is oorspronkelijk ontwikkeld door Intel en vervolgens gedoneerd aan de bredere UCIe-groep om als basis te dienen voor een nieuwe standaard. Maar de bedrijven die lid zijn van de groep “zullen later dit jaar gaan samenwerken aan de volgende generatie UCIe-technologie”.

Als u meer technische details over de UCIe-standaard nodig heeft, kunt u de whitepaper hier vinden .

Afbeeldingslijst van AMD

Geef een reactie