Intel, AMD i inni potentaci branży tworzą nowy standard chipletów

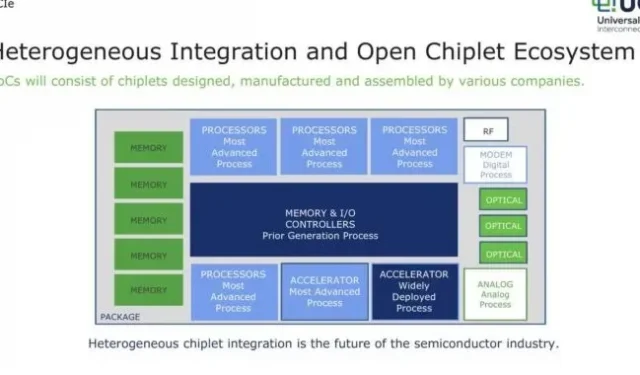

Niektórzy z największych producentów procesorów, w tym Intel, AMD, Qualcomm, Arm, TSMC i Samsung, łączą siły, aby zdefiniować nowy standard dla procesorów opartych na chipach. Nowy standard, nazwany Universal Chiplet Interconnect Express (w skrócie UCIe), ma na celu zdefiniowanie otwartego, interoperacyjnego standardu łączenia wielu matryc krzemowych (lub chipletów) w jedną obudowę.

Intel, AMD i inni już opracowują lub sprzedają procesory oparte na chipletach w takiej czy innej formie — większość procesorów AMD Ryzen korzysta z chipletów, a przyszłe procesory Intel Sapphire Rapids Xeon również będą. Ale wszystkie te chipy używają różnych połączeń, aby umożliwić komunikację między chipletami. Standard UCIe, jeśli się powiedzie, zastąpi je jednym standardem, teoretycznie ułatwiając małym firmom korzystanie z chipsetów lub wykorzystywanie chipów innej firmy we własnych produktach.

Konstrukcje oparte na chipach są korzystne dla produkcji dużych chipów w zaawansowanych zakładach produkcyjnych, po części dlatego, że zmniejszają ilość krzemu, który producenci muszą marnować. Jeśli wada produkcyjna dotyczy jednego rdzenia procesora, wyrzucenie (lub usunięcie) jednego 8-rdzeniowego chipletu jest znacznie tańsze niż wyrzucenie ogromnej 16- lub 32-rdzeniowej kości procesora. Projekty układów scalonych umożliwiają również łączenie układów scalonych i procesów produkcyjnych. Na przykład możesz użyć starszego, tańszego procesu dla swojego chipsetu i nowszego, bardziej zaawansowanego procesu dla rdzeni procesora i pamięci podręcznych. Lub możesz umieścić procesor graficzny AMD w tej samej obudowie, co procesor Intel.

Według AnandTech standard UCIe obejmie fizyczne i protokołowe warstwy projektowania układów scalonych. Standard określi, w jaki sposób chiplety powinny być ze sobą połączone, oraz protokół ułatwiający komunikację między chipletami. Jednak projektanci układów scalonych będą mogli dowolnie pakować te układy w sposób, jaki uznają za stosowny, umożliwiając układom komunikowanie się ze sobą bezpośrednio przez podłoże opakowania lub przy użyciu mostka na bazie krzemu lub innego pośrednika.

Aby uwzględnić te różne opcje pakowania fizycznego, UCIe w wersji 1.0 definiuje dwa różne poziomy wydajności. Pakiet „Standardowy” wymaga 16 pasów danych i do 25 mm odstępu między chipsetami, podczas gdy pakiet „Rozszerzony” wykorzystuje 64 tory danych i pozostawia tylko 2 mm miejsca.

Protokoły leżące u podstaw UCIe to PCI Express i powiązane standardy Compute Express Link (CXL), które są dobrze znane producentom chipów. Ale firmy, które opracowały już bardziej zaawansowane lub dedykowane protokoły do komunikacji między chipsetami, takie jak AMD i jej Infinity Fabric , będą mogły korzystać z tych protokołów, zachowując zgodność z UCIe. UCIe został pierwotnie opracowany przez firmę Intel, a następnie przekazany szerszej grupie UCIe jako podstawa nowego standardu. Ale firmy członkowskie grupy „rozpoczną współpracę nad technologią nowej generacji UCIe” jeszcze w tym roku.

Jeśli potrzebujesz więcej szczegółów technicznych na temat standardu UCIe, możesz znaleźć białą księgę tutaj .

Lista obrazów od AMD

Dodaj komentarz