Intel, AMD och andra tungviktare i branschen skapar en ny chiplet-standard

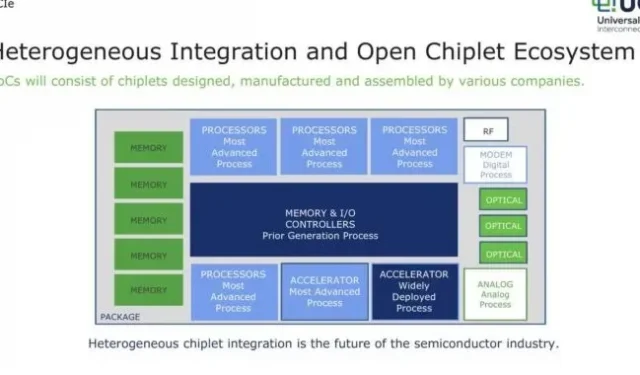

Några av de största processortillverkarna, inklusive Intel, AMD, Qualcomm, Arm, TSMC och Samsung, går ihop för att definiera en ny standard för chipbaserade processorer. Den nya standarden, kallad Universal Chiplet Interconnect Express (UCIe för kort), syftar till att definiera en öppen, interoperabel standard för att kombinera flera kiselformar (eller chiplets) i ett enda paket.

Intel, AMD och andra utvecklar eller säljer redan chipletbaserade processorer i en eller annan form – de flesta AMD Ryzen-processorer använder chiplets, och framtida Intel Sapphire Rapids Xeon-processorer kommer också att göra det. Men alla dessa chip använder olika sammankopplingar för att möjliggöra kommunikation mellan chipletarna. UCIe-standarden, om den lyckas, kommer att ersätta dem med en enda standard, vilket teoretiskt gör det lättare för små företag att använda chipset eller använda ett annat företags chips i sina egna produkter.

Chipbaserade konstruktioner är fördelaktiga för tillverkning av stora spån vid avancerade tillverkningsanläggningar, delvis för att de minskar mängden kisel som tillverkarna måste slösa. Om ett tillverkningsfel påverkar en CPU-kärna, är det mycket billigare att slänga (eller ta bort) en 8-kärnig chiplet än att slänga en enorm 16- eller 32-kärnig CPU-där. Chipdesign tillåter också kombinationen av chips och tillverkningsprocesser. Du kan till exempel använda en äldre, billigare process för din chipset och en nyare, mer avancerad process för processorkärnor och cachar. Eller så kan du sätta en AMD GPU i samma fodral som en Intel-processor.

Enligt AnandTech kommer UCIe-standarden att täcka de fysiska och protokollskikten av chipdesign. Standarden kommer att definiera hur chiplets ska kopplas till varandra och ett protokoll för att underlätta kommunikationen mellan chiplets. Men chipdesigners kommer att vara fria att paketera dessa chiplets hur de vill, vilket gör att chipletarna kan kommunicera med varandra direkt genom paketets substrat eller genom att använda någon form av kiselbaserad brygga eller annan mellanhand.

För att ta hänsyn till dessa olika fysiska förpackningsalternativ, definierar UCIe version 1.0 två olika prestandanivåer. ”Standard”-paketet kräver 16 datafält och upp till 25 mm utrymme mellan chipset, medan det ”Utökade”-paketet använder 64 datafält och tillåter endast 2 mm utrymme.

Protokollen som ligger till grund för UCIe är PCI Express och relaterade Compute Express Link-standarder (CXL), som är välkända för chiptillverkarna. Men företag som redan har utvecklat mer avancerade eller dedikerade protokoll för kommunikation mellan chipset, som AMD och dess Infinity Fabric , kommer att kunna använda dessa protokoll samtidigt som de förblir UCIe-kompatibla. UCIe utvecklades ursprungligen av Intel och donerades sedan till den bredare UCIe-gruppen för att fungera som grunden för en ny standard. Men gruppens medlemsföretag ”kommer att börja arbeta tillsammans på nästa generations UCIe-teknik” med start senare i år.

Om du behöver mer teknisk information om UCIe-standarden hittar du vitboken här .

Bildlista från AMD

Lämna ett svar