Intels största CPU-uppdatering för bärbara datorer på flera år är en enorm avvikelse från tidigare design

Intels nästa generations bärbara Meteor Lake-processorer närmar sig lanseringen – företaget meddelade denna vecka att de första processorerna kommer att lanseras den 14 december. Det är oklart om faktiska Core- och Core Ultra-system kommer att vara tillgängliga att köpa på det datumet, men som ett absolut minimum , kommer det officiella tillkännagivandet att bana väg för många meddelanden om bärbara datorer på CES i januari.

Vi vet redan en hel del grundläggande fakta om Meteor Lake; den använder en kombination av chiplets tillverkade av både Intel och TSMC snarare än en enda monolitisk form, och det kommer att markera pensioneringen av Intels ”n:te generationens” och i3/i5/i7/i9 varumärke. Vi vet också att det inte kommer att vara redo för stationära datorer och att nästa omgång av Core-datorprocessorer kommer att vara mycket lik 12:e och 13:e generationens chips.

Men vid Intels innovationsevent den här veckan gick företaget lite djupare in i några av Meteor Lakes framsteg, och beskrev mer om hur chipsen skulle balansera E-kärnor och P-kärnor och tillkännagav sin mest betydande integrerade GPU-uppgradering på flera år. Vi kommer att träffa några höjdpunkter nedan, även om det är värt att titta på eller läsa hela presentationen för att få veta mer.

Kakel för mil

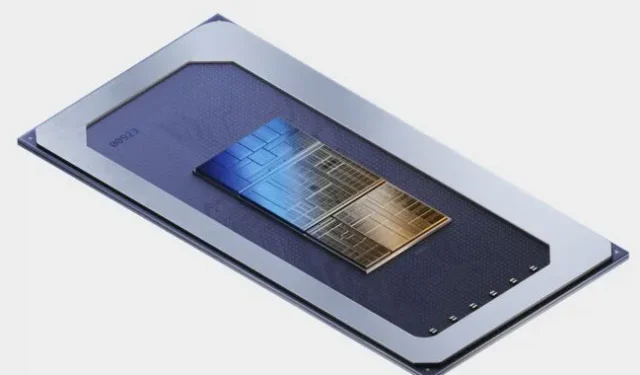

Meteor Lake kommer att vara Intels första konsumentprocessor som går över till en chiplet-baserad design – istället för att vara en monolitisk platta som innehåller CPU, GPU och alla andra bitar och delar som behövs för en modern bärbar CPU, är Meteor Lake uppdelad i fyra ”plattor” som är sammanfogade av en femte basplatta som gör att de kan kommunicera med varandra. Processen att stapla chipletarna ovanpå basplattan är en förpackningsteknik som Intel kallar Foveros .

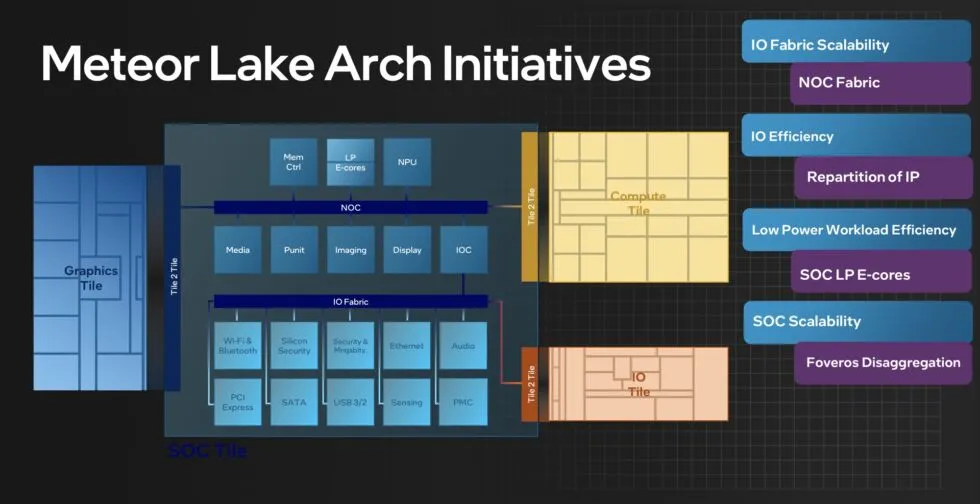

Här är en grundläggande uppdelning av vad som finns i var och en av dessa fyra brickor:

- Beräkningsplattan är där det mesta av den faktiska CPU:n finns . Intels nuvarande renderingar visar ett chip med sex högpresterande P-kärnor baserade på Redwood Cove-arkitekturen och åtta högeffektiva E-kärnor baserade på Crestmont-arkitekturen.

- Grafikpanelen är där den mesta grafikbearbetningen sker, även om några specifika funktioner som du vanligtvis hittar i en GPU har flyttats till andra brickor . Meteor Lakes integrerade GPU är för det mesta bara en integrerad version av en Intel Arc-dedikerad GPU, komplett med hårdvaru-ray-tracing-acceleration.

- IO- brickan hanterar de flesta externa anslutningar, inklusive PCI Express 5.0-banor och Thunderbolt 4-stöd ( Thunderbolt 5 måste vänta).

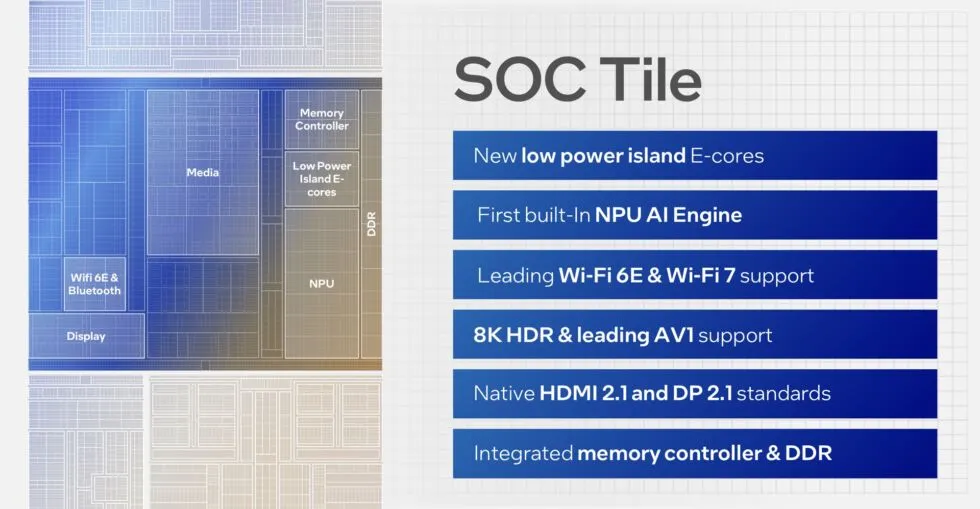

- SoC -brickan är förmodligen den mest intressanta av de fyra. Den innehåller ytterligare två Crestmont E-kärnor, mediakodnings- och avkodningsmotorn som normalt skulle finnas i GPU:n och den neurala bearbetningsenheten (NPU) som används för att accelerera AI och maskininlärning. Den hanterar även Wi-Fi och Bluetooth-anslutning och anslutning till externa skärmar över HDMI 2.1 och DisplayPort 2.1.

En av de anmärkningsvärda sakerna med Meteor Lake är att inte alla brickor tillverkas av Intel. Beräkningsplattan, som innehåller de faktiska P-kärnorna och de flesta av E-kärnorna, använder den nya Intel 4-processen, en uppgradering från Intel 7-processen som används för de flesta aktuella Core-chips. Men grafikplattan görs på en 5 nm TSMC-process, medan IO-plattan och SoC-plattan är gjorda på en 6 nm TSMC-process.

Intel har också använt TSMC:s tillverkning för att göra sina Arc GPU:er, så det är inte första gången vi har sett dessa två chipframställningsfrenemies arbeta tillsammans. Men Intel försöker komma ikapp TSMC:s tillverkning, och Intel ser dess gjuteriverksamhet som nyckeln till dess framtida tillväxt. Jag skulle inte bli förvånad om det slutliga målet är att flytta tillbaka till helt Intel-tillverkade brickor.

Ännu fler E-kärnor

Intel har sagt att Meteor Lakes P-kärnor inte förändras mycket jämfört med de som används i 12:e och 13:e generationens Alder Lake och Raptor Lake CPU:er – vi kan se högre klockhastigheter, men inte mycket har förändrats när det gäller instruktioner – per klocka eller instruktionsuppsättning. E-kärnorna får dock vissa förbättringar.

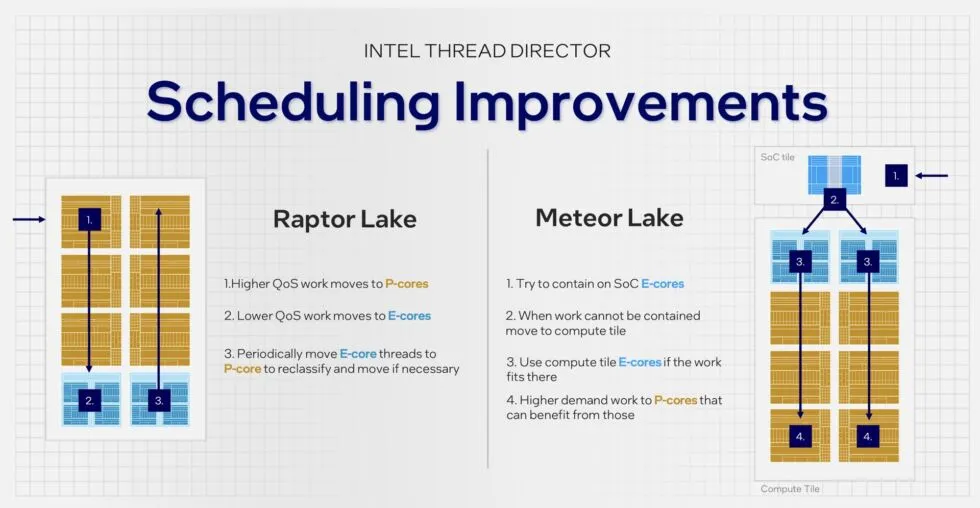

Meteor Lake innehåller faktiskt två olika typer av E-kärnor. Det finns två E-kärnor med låg effekt (LP) i SoC-panelen, och den uppdaterade versionen av Intels Thread Director kommer att försöka använda dessa E-kärnor för så många uppgifter som möjligt. Intel kallar denna del av SoC-brickan för ”lågeffektsön” eftersom tanken är att låta beräkningsplattan och grafikpanelen stängas av helt så mycket som möjligt för att spara ström.

När uppgifter kräver mer prestanda än vad LP E-cores kan ge, kommer Thread Director att sparka dem till beräkningspanelen – antingen till de viktigaste E-core-klustren, som är inställda för att hantera flertrådiga arbetsbelastningar med låg effekt, eller till P-kärnorna , som används för enkeltrådade uppgifter och eventuellt flertrådsarbete som E-kärnorna inte kan hantera. Detta är en förändring från hur Thread Director fungerar i 12:e och 13:e generationens processorer, där högprioriterade uppgifter skulle gå direkt till P-kärnorna utan att prova E-kärnorna först. (Även om det återstår att se om Thread Director-ändringarna kommer att resultera i någon form av användaren märkbara förseningar för högpresterande uppgifter.)

Också värt att notera: Crestmont E-kärnor kan läggas till processorer i grupper om två, där tidigare generation Gracement E-kärnor bara kunde läggas till i grupper om fyra. Detta kan göra det lättare för Intel att motivera att ta små grupper av E-kärnor till lägre processorer som inte hade dem tidigare. Alla E-kärnor förblir enkelgängade, medan P-kärnor fortfarande stöder två trådar per kärna.

De nya E-kärnorna inkluderar också några andra snällheter – VNNI-instruktioner för att accelerera AI-arbetsbelastningar och till och med AVX10, som ger många av fördelarna med Intels AVX-512-instruktioner utan att kräva 512-bitarsregister. 12:e och 13:e generationens Core-processorer stängde helt av AVX-512-stödet eftersom E-kärnorna inte stödde det, även om stöd fanns i P-kärnorna. Detta har skapat en besvärlig situation där AMD:s senaste Zen 4-chips stödjer AVX-512-instruktionerna som Intel uppfann och marknadsförde, där Intels senaste konsumentchips inte gör det.

Lämna ett svar