英特爾、AMD 和其他行業巨頭正在創建新的小芯片標準

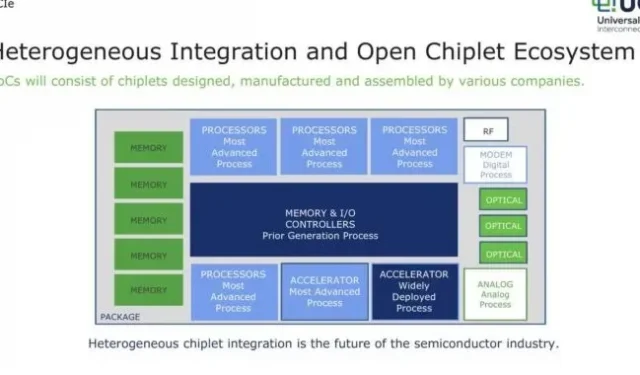

一些最大的處理器製造商,包括英特爾、AMD、高通、Arm、台積電和三星,正在聯手為基於芯片的處理器定義新標準。新標準稱為Universal Chiplet Interconnect Express(簡稱UCIe),旨在定義一個開放的、可互操作的標準,用於將多個矽芯片(或小芯片)組合到單個封裝中。

英特爾、AMD 和其他公司已經以某種形式開發或銷售基於小芯片的處理器——大多數 AMD Ryzen 處理器都使用小芯片,未來的英特爾 Sapphire Rapids Xeon 處理器也將使用。但所有這些芯片都使用不同的互連來實現小芯片之間的通信。UCIe標準如果成功,將用單一標準取代它們,理論上使小公司更容易在自己的產品中使用芯片組或使用其他公司的芯片。

基於芯片的設計有利於先進製造工廠的大型芯片製造,部分原因是它們減少了製造商浪費的矽量。如果製造缺陷影響一個 CPU 核心,則丟棄(或移除)一個 8 核小芯片比丟棄一個巨大的 16 核或 32 核 CPU 芯片要便宜得多。芯片設計還允許芯片和製造工藝的結合。例如,您可以為芯片組使用較舊、更便宜的工藝,為處理器核心和緩存使用更新、更先進的工藝。或者您可以將 AMD GPU 與 Intel 處理器放在同一個機箱中。

AnandTech表示,UCIe 標準將覆蓋芯片設計的物理層和協議層。該標準將定義小芯片如何相互連接以及促進小芯片之間通信的協議。但芯片設計人員可以自由地以他們認為合適的方式封裝這些小芯片,從而允許小芯片直接通過封裝基板或使用某種矽基橋或其他中介相互通信。

為了考慮到這些不同的物理封裝選項,UCIe 1.0 版定義了兩種不同的性能級別。“標準”封裝需要 16 個數據通道和芯片組之間最多 25 毫米的空間,而“擴展”封裝則使用 64 個數據通道,並且只允許 2 毫米的空間。

UCIe 的底層協議是芯片製造商熟知的 PCI Express 和相關的 Compute Express Link (CXL) 標準。但是,那些已經開發出更先進或專用的芯片組之間通信協議的公司(例如AMD 及其 Infinity Fabric)將能夠使用這些協議,同時保持 UCIe 合規性。UCIe 最初由英特爾開發,然後捐贈給更廣泛的 UCIe 小組作為新標準的基礎。但從今年晚些時候開始,該集團的成員公司“將開始共同開發下一代 UCIe 技術”。

如果您需要有關 UCIe 標準的更多技術細節,可以在此處找到白皮書。

來自AMD 的圖片列表

發佈留言