Intel, AMD та інші важковаговики галузі створюють новий стандарт мікросхем

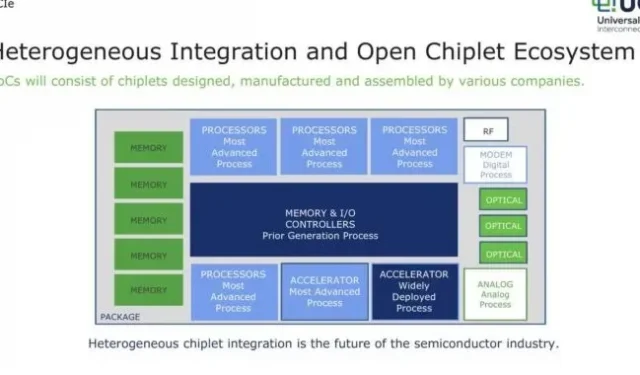

Деякі з найбільших виробників процесорів, зокрема Intel, AMD, Qualcomm, Arm, TSMC і Samsung, об’єднуються, щоб визначити новий стандарт для процесорів на базі мікросхем. Новий стандарт під назвою Universal Chiplet Interconnect Express (скорочено UCIe) спрямований на визначення відкритого, сумісного стандарту для об’єднання кількох кремнієвих кристалів (або чіплетів) в один пакет.

Intel, AMD та інші вже розробляють або продають процесори на основі мікросхем у тій чи іншій формі — більшість процесорів AMD Ryzen використовують мікросхеми, і майбутні процесори Intel Sapphire Rapids Xeon також будуть. Але всі ці мікросхеми використовують різні з’єднання для забезпечення зв’язку між мікросхемами. Стандарт UCIe, якщо він досягне успіху, замінить їх єдиним стандартом, теоретично полегшивши невеликим компаніям використання чіпсетів або використання чіпів інших компаній у власних продуктах.

Конструкції на основі чіпів є корисними для виготовлення великих чіпів на передових виробничих майданчиках, частково тому, що вони зменшують кількість кремнію, який виробники повинні витрачати. Якщо виробничий дефект впливає на одне ядро ЦП, викинути (або видалити) один 8-ядерний чіплет набагато дешевше, ніж викинути величезний 16- або 32-ядерний процесор. Конструкції чіпів також дозволяють поєднувати чіпи та виробничі процеси. Наприклад, ви можете використовувати старіший, дешевший процес для свого чіпсета та новіший, досконаліший процес для процесорних ядер і кеш-пам’яті. Або ви можете помістити графічний процесор AMD в один корпус із процесором Intel.

За словами AnandTech , стандарт UCIe охоплюватиме фізичний і протокольний рівні дизайну мікросхем. Стандарт визначатиме, як чіплети повинні бути з’єднані один з одним, і протокол для полегшення зв’язку між чіплетами. Але розробники чіпів будуть вільні упаковувати ці чіплети так, як вони вважають за потрібне, дозволяючи чіплетам спілкуватися один з одним безпосередньо через підкладку упаковки або використовуючи якийсь міст на основі кремнію чи інший посередник.

Щоб врахувати ці різні варіанти фізичного пакування, UCIe версії 1.0 визначає два різні рівні продуктивності. Пакет «Стандарт» вимагає 16 смуг даних і до 25 мм простору між чіпсетами, тоді як пакет «Extended» використовує 64 смуги даних і дозволяє лише 2 мм простору.

Протоколи, що лежать в основі UCIe, — це PCI Express і відповідні стандарти Compute Express Link (CXL), які добре відомі виробникам мікросхем. Але компанії, які вже розробили вдосконалені або спеціальні протоколи для зв’язку між чіпсетами, такі як AMD і її Infinity Fabric , зможуть використовувати ці протоколи, залишаючись сумісними з UCIe. UCIe спочатку був розроблений Intel, а потім переданий ширшій групі UCIe, щоб стати основою для нового стандарту. Але компанії-члени групи «почнуть співпрацювати над технологією наступного покоління UCIe» пізніше цього року.

Якщо вам потрібні додаткові технічні відомості про стандарт UCIe, ви можете знайти офіційний документ тут .

Список зображень від AMD

Залишити відповідь