Intel, AMD e outros pesos pesados da indústria estão criando um novo padrão de chiplet

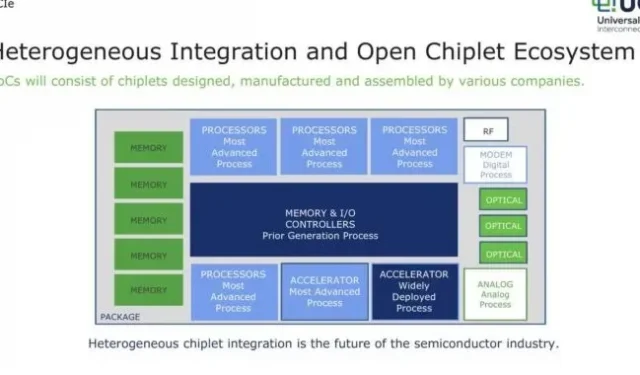

Alguns dos maiores fabricantes de processadores, incluindo Intel, AMD, Qualcomm, Arm, TSMC e Samsung, estão se unindo para definir um novo padrão para processadores baseados em chip. O novo padrão, chamado Universal Chiplet Interconnect Express (UCIe para abreviar), visa definir um padrão aberto e interoperável para combinar várias matrizes de silício (ou chiplets) em um único pacote.

Intel, AMD e outros já estão desenvolvendo ou vendendo processadores baseados em chiplet de uma forma ou de outra – a maioria dos processadores AMD Ryzen usa chiplets, e os futuros processadores Intel Sapphire Rapids Xeon também o farão. Mas todos esses chips usam interconexões diferentes para permitir a comunicação entre os chiplets. O padrão UCIe, se for bem-sucedido, os substituirá por um único padrão, teoricamente tornando mais fácil para pequenas empresas usar chipsets ou usar chips de outras empresas em seus próprios produtos.

Os projetos baseados em chips são benéficos para a fabricação de chips grandes em locais de fabricação avançados, em parte porque reduzem a quantidade de silício que os fabricantes precisam desperdiçar. Se um defeito de fabricação afetar um núcleo da CPU, jogar fora (ou remover) um chiplet de 8 núcleos é muito mais barato do que jogar fora uma enorme matriz de CPU de 16 ou 32 núcleos. Os projetos de chips também permitem a combinação de chips e processos de fabricação. Por exemplo, você pode usar um processo mais antigo e mais barato para o seu chipset e um processo mais novo e avançado para os núcleos e caches do processador. Ou você pode colocar uma GPU AMD no mesmo gabinete de um processador Intel.

De acordo com a AnandTech , o padrão UCIe cobrirá as camadas físicas e de protocolo do design do chip. O padrão definirá como os chiplets devem ser conectados entre si e um protocolo para facilitar a comunicação entre os chiplets. Mas os projetistas de chips estarão livres para empacotar esses chiplets da maneira que acharem melhor, permitindo que os chiplets se comuniquem diretamente através do substrato do pacote ou usando algum tipo de ponte baseada em silício ou outro intermediário.

Para levar em conta essas diferentes opções de embalagem física, o UCIe versão 1.0 define dois níveis diferentes de desempenho. O pacote “Standard” requer 16 pistas de dados e até 25 mm de espaço entre os chipsets, enquanto o pacote “Estendido” usa 64 pistas de dados e permite apenas 2 mm de espaço.

Os protocolos subjacentes ao UCIe são o PCI Express e os padrões Compute Express Link (CXL) relacionados, que são bem conhecidos pelos fabricantes de chips. Mas as empresas que já desenvolveram protocolos mais avançados ou dedicados para comunicação entre chipsets, como AMD e seu Infinity Fabric , poderão usar esses protocolos enquanto permanecem compatíveis com UCIe. O UCIe foi originalmente desenvolvido pela Intel e depois doado ao grupo UCIe mais amplo para servir de base para um novo padrão. Mas as empresas membros do grupo “começarão a trabalhar juntas na tecnologia UCIe de próxima geração” a partir do final deste ano.

Se precisar de mais detalhes técnicos sobre o padrão UCIe, você pode encontrar o white paper aqui .

Listagem de imagens da AMD

Deixe um comentário